# September 28, 2012 RDm037D

# **Quad Operational Amplifiers**

αRD148/N5B, αRD148/B5B, αRD148/Z5B, αRD148/Z7B αRD149/N5B, αRD149/B5B, αRD149/Z5B, αRD149/Z7B

## **General Description**

The  $\alpha$ RD148/149 is a true quad 741. It consists of four independent, high gains, internally compensated, low power operational amplifiers which have been designed to provide functional characteristics identical to those of the classic 741 operational amplifier. In addition the total supply current for all four amplifiers is comparable to the supply current of a single 741 type op amp. Other features include input offset currents and input bias current which are much less than those of a standard 741. Also, excellent isolation between amplifiers has been achieved by independently biasing each amplifier and using layout techniques which minimize thermal coupling. The  $\alpha$ RD149 series has the same features as the  $\alpha$ RD148 plus a gain bandwidth product of 4 MHz at a gain of 5 or greater.

The  $\alpha$ RD148/149 can be used anywhere multiple 741 type amplifiers are being used and in applications where amplifier matching or high packing density is required. These amplifiers have been developed and certified as HiRel and RadHard components for airspace and defense equipment. High reliability is ensured by microcircuit manufacturing process, briefly described in the section "Process Flow" (Figure 1). Radiation tolerance is not less than 100 kRad (Si).

The  $\alpha$ RD148/149 is in conformity with Directive 2011/65/EU of 8 June 2011 and don't use hazardous substances.

#### **Features**

- 741 op amp operating characteristics

- Class AB output stage—no crossover distortion

- Overload protection for inputs and outputs

- Low supply current drain: 0.6 mA/Amplifier

- Low input offset voltage: 1 mV

- Low input offset current: 4 nA

- Low input bias current 30 nA

- High degree of isolation between amplifiers:

120 dB

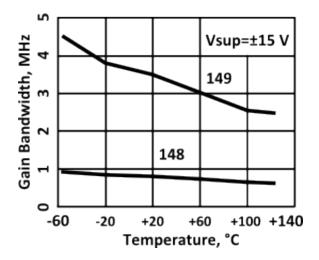

- Gain bandwidth product αRD148 (AV=1): 1.0 MHz αRD149 (AV≥ 5): 4 MHz

# **Applications**

- Data Acquisition Systems

- Analogue Filters

- Instrumentation Amplifiers

- RF Amplifiers

- Video Amplifiers

- Signal Generators

- Pulse Amplification

# **Ordering information**

| Part                     | Temp., °C | Package | Package<br>drawing |  |

|--------------------------|-----------|---------|--------------------|--|

| αRD148/N5B               |           | 14-lead | CSOF-              |  |

| αRD149/N5B               |           | Flat    | 14                 |  |

| αRD148/B5B               |           | 14-lead | CDIP-14            |  |

| αRD149Z5B                | -60 to    | Dip     |                    |  |

| αRD148/Z5B<br>αRD148/Z7B | +125      | 20-lead | CQFN-              |  |

| αRD149/Z5B<br>αRD149/Z7B |           | CLCC    | 20                 |  |

### **Pin Function Descriptions**

| Description                | Maaaaaia         | Pin No  |         |         |  |

|----------------------------|------------------|---------|---------|---------|--|

| Description                | Mnemonic         | CSOF-14 | CDIP-14 | CQFN-20 |  |

| Output amplifier 1         | OUT1             | 1       | 1       | 2       |  |

| Negative input amplifier 1 | -IN1             | 2       | 2       | 3       |  |

| Positive input amplifier 1 | +IN1             | 3       | 3       | 4       |  |

| Positive supply            | V <sub>S</sub> + | 4       | 4       | 6       |  |

| Positive input amplifier 2 | +IN2             | 5       | 5       | 8       |  |

| Negative input amplifier 2 | -IN2             | 6       | 6       | 9       |  |

| Output amplifier 2         | OUT2             | 7       | 7       | 10      |  |

| Output amplifier 3         | OUT3             | 8       | 8       | 12      |  |

| Negative input amplifier 3 | -IN3             | 9       | 9       | 13      |  |

| Positive input amplifier 3 | +IN3             | 10      | 10      | 14      |  |

| Negative supply            | V <sub>S</sub> - | 11      | 11      | 16      |  |

| Positive input amplifier 4 | +IN4             | 12      | 12      | 18      |  |

| Negative input amplifier 4 | -IN4             | 13      | 13      | 19      |  |

| Output amplifier 4         | OUT4             | 14      | 14      | 20      |  |

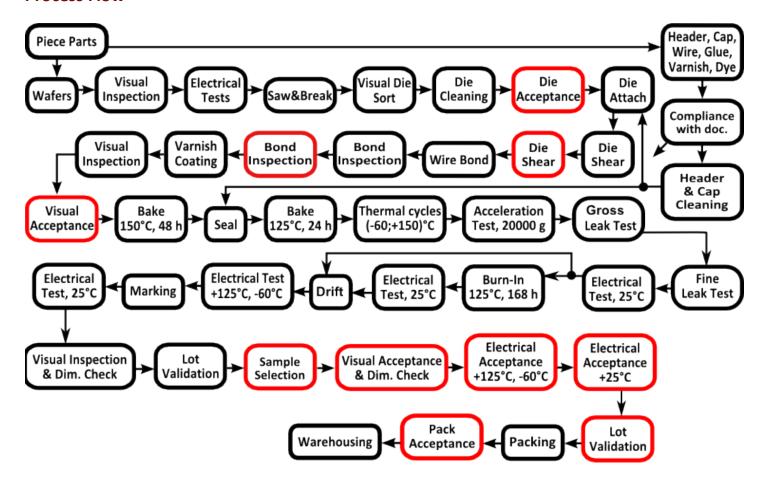

#### **Process Flow**

### Notes:

1. Color shows the quality assurance procedures

Figure 1. Process Flow

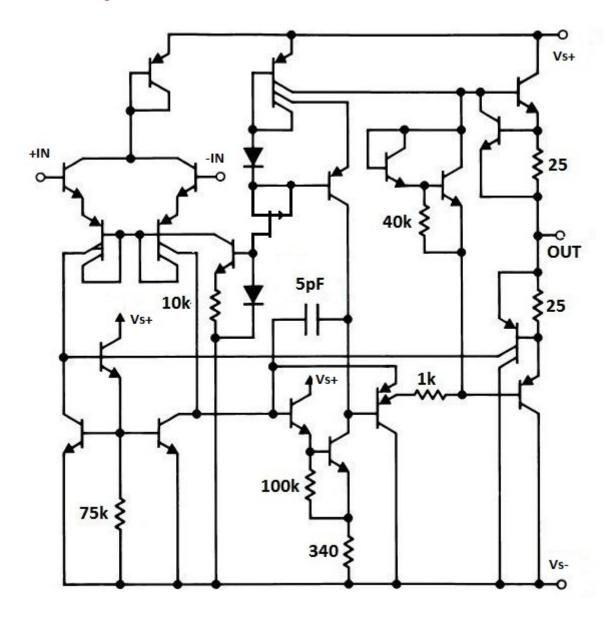

# **Schematic Diagram**

## Notes:

2. In the  $\alpha$ RD149, 1pF instead of 5 pF

Figure 2.  $\alpha$ RD148,  $\alpha$ RD 149 Schematic Diagram (1/4 IC)

### **Absolute Maximum Ratings**

### **Thermal Information**

Thermal Resistance (typical)(note 6)  $\theta_{JA} = 25 \text{ °C/W (CDIP-14)}$   $\theta_{JA} = 60 \text{ °C/W (CSOF-14)}$  Maximum Junction Temperature +175 °C Lead Temperature (soldering 3 s) 350 °C

## **Operation Condition**

Operating Temperature Range -60 °C to +125 °C Storage Temperature Range -65 °C to +150 °C Operating Supply Voltage  $\pm$  15 V  $\pm$ 10 % Allowable load R<sub>L</sub>  $\geq$ 2 k $\Omega$  ESD Tolerance (note 5) 500 V

#### Notes:

- 3. The maximum power dissipation for these devices must be derated at elevated temperatures and is dictated by  $T_{JMAX}$ ,  $\theta_{JA}$ , and the ambient temperature  $T_A$ . The maximum available power dissipation at any temperature is  $P_d = (T_{JMAX} T_A)/\theta_{JA}$  or the number given in the Absolute Maximum Ratings, whichever is less.

- 4. Any of the amplifier outputs can be shorted to ground indefinitely; however, more than one should not be simultaneously shorted as the maximum junction temperature will be exceeded.

- 5. Human body model, 1.5 k $\Omega$  in series with 100 pF.

- 6.  $\theta_{JA}$  is measured with component on an evaluation PC board in free air.

# **Electrical Specifications**

V<sub>SUPPLY</sub> = ± 15 V ± 1 % (unless otherwise specified)

| Davamatav                           | Taman 86    | αRD148 |      | αRD149 |      |                |  |

|-------------------------------------|-------------|--------|------|--------|------|----------------|--|

| Parameter                           | Temp., °C   | Min    | Max  | Min    | Max  | Unit           |  |

| Input Characteristics               |             |        |      |        |      |                |  |

|                                     | 25          | -5     | +5   | -5     | +5   |                |  |

| Input Offset Voltage                | +125        | -6     | +6   | -6     | +6   | mV             |  |

|                                     | -60         | -6     | +6   | -6     | +6   |                |  |

| Input Offset Voltage Drift          | -60 to +25  | -      | 0.2  | -      | 0.2  | V/°C           |  |

| (note 7)                            | +25 to +125 | -      | 0.1  | -      | 0.1  | <b>-</b> μV/°C |  |

|                                     | 25          | 1      | 100  | 1      | 100  | nA             |  |

| Input Bias Current                  | +125        | 1      | 100  | 1      | 100  |                |  |

|                                     | -60         | 1      | 325  | 1      | 325  |                |  |

|                                     | 25          | -25    | +25  | -25    | +25  |                |  |

| Input Offset Current                | +125        | -25    | +25  | -25    | +25  | nA             |  |

|                                     | -60         | -75    | +75  | -75    | +75  |                |  |

| Input Offset Current Drift (note 7) | -60 to +25  | -      | 0.25 | -      | 0.25 | nA/°C          |  |

|                                     | +25 to +125 | -      | 0.25 | -      | 0.25 |                |  |

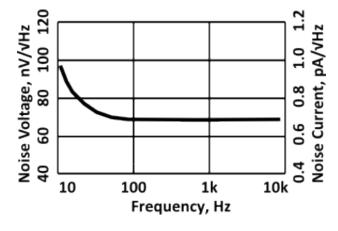

| Noise                               |             |        |      |        |      |                |  |

| Broadband Noise (note 15)           | 25          | -      | 15   | -      | 15   | $\mu V_{RMS}$  |  |

| Popcorn Noise                       | 25          | -      | 40   | -      | 40   | $\mu V_{PK}$   |  |

| Donomoton                                 | Tama °C   | αRD148    |      | αRD149 |      | 11   |

|-------------------------------------------|-----------|-----------|------|--------|------|------|

| Parameter                                 | Temp., °C | Min       | Max  | Min    | Max  | Unit |

| Output Characteristics                    |           |           |      |        |      |      |

| Maximum Output Voltage (note 8)           | 25        | 9.5       | -    | 9.5    |      |      |

|                                           | +125      | 9.0       | -    | 9.0    |      | V    |

|                                           | -60       | 9.0       | -    | 9.0    |      |      |

| Naining on Contract Valte on              | 25        | -         | -9.5 | -      | -9.5 |      |

| Minimum Output Voltage (note 8)           | +125      | -         | -9.0 | -      | -9.0 | V    |

| (note 8)                                  | -60       | -         | -9.0 | -      | -9.0 |      |

| Source and Drain Short<br>Circuit Current | 25        | -55       | -14  | -55    | -14  | mA   |

| Transfer Characteristics                  |           |           |      |        |      |      |

| Lana Ciaral Vallara Caia                  | 25        | 50        | -    | 50     | -    |      |

| Large Signal Voltage Gain (note 8, 11)    | +125      | 25        | -    | 25     | -    | V/mV |

| (note 8, 11)                              | -60       | 25        | -    | 25     | -    |      |

| Common Mada Daiastian                     | 25        | 70        | -    | 70     | -    |      |

| Common Mode Rejection Ratio (note 12)     | +125      | 70        | -    | 70     | -    | dB   |

| Natio (note 12)                           | -60       | 70        | -    | 70     | -    |      |

| Davier Consolio Dalastico                 | 25        | 77        | -    | 77     | -    | dB   |

| Power Supply Rejection<br>Ratio (note 13) | +125      | 77        | -    | 77     | -    |      |

| Natio (note 13)                           | -60       | 77        | -    | 77     | -    |      |

| Channel Separation (note 11, 14)          | 25        | 80        | -    | 80     | -    | dB   |

| Dynamic Characteristics                   |           |           |      |        |      |      |

| Slew rate (note 10, 16)                   | 25        | 0.2       | -    | 2      | -    | V/µs |

| Gain Bandwidth Product (note 8)           | 25        | 0.4       | -    | 3.4    | -    | MHz  |

| Power Supply                              | <u> </u>  |           |      |        |      |      |

|                                           | 25        | _         | 4.6  | _      | 4.6  | mA   |

| Supply Current (note 17)                  | +125      | _         | 4.6  | -      | 4.6  |      |

|                                           | -60       | -         | 5.5  | -      | 5.5  |      |

| Drift (αRD148XR7U and αRD                 |           | (note 18) | _    |        |      |      |

| Input Offset Voltage                      | 25        | -1        | 1    | -1     | 1    | mV   |

| Input Bias Current                        | 25        | -15       | 15   | -15    | 15   | nA   |

#### Notes:

- 7. Calculated parameter

- 8.  $R_L = 2 k\Omega$

- 9.  $V_{OUT} = \pm 200 \text{ mV}$

- 10.  $V_{OUT} = \pm 5 V$

- 11.  $V_{OUT} = \pm 10 \text{ V}$

- 12.  $V_{CM} = \pm 12 V$

- 13.  $\pm 5 \text{ V} \leq V_{SUPPLY} \leq \pm 15 \text{ V}$

- 14. In any combination, 20 Hz to 20 kHz

- 15. 10 Hz to 5 kHz

- 16. 148: A<sub>V</sub>=1, 149: A<sub>V</sub>=5

- 17. All amplifier

- 18. Measure each amplifier

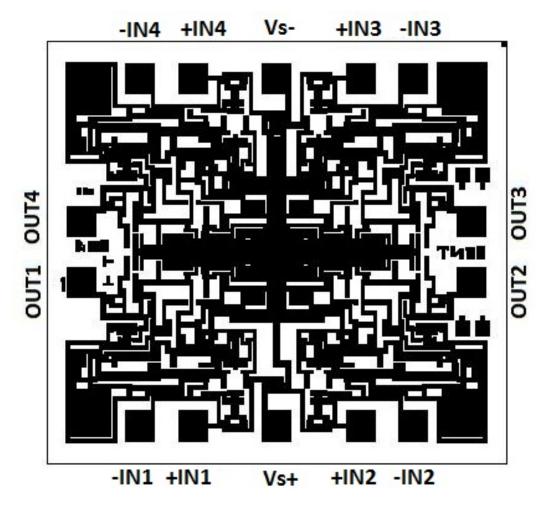

### **Die Characteristics**

Die dimensions:  $2.1x1.8 \pm 0.1$  mm. Wafer thickness:  $0.46 \pm 0.02$  mm.

Metallization: Al, 1% Si, thickness: 1.4  $\pm$  0.1  $\mu m.$

Glassivation: phosphosilicate glass (PSG),

thickness 1.2  $\pm$  0.2  $\mu$ m.

Worst case current density: 800 A/mm<sup>2</sup>.

Substrate potential: Unbiased.

Transistor count: 94.

Process: bipolar epitaxial.

# **Metallization Mask Layout**

Figure 3. Metallization mask and pin-outs

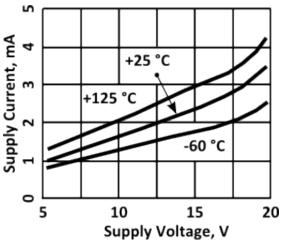

# **Typical Performance Characteristics**

Figure 5. Supply Current vs Supply Voltage

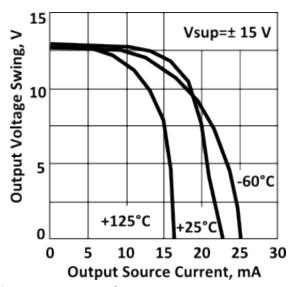

Figure 7. Output Voltage vs Output Source Current

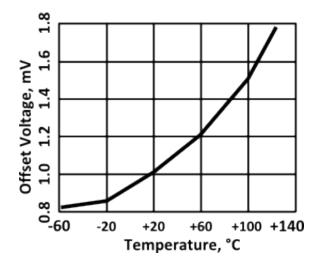

Figure 9. Offset Voltage vs Temperature

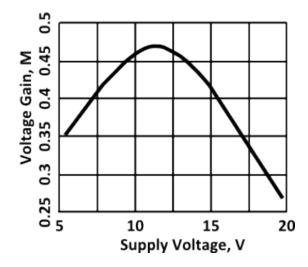

Figure 6. Open Loop Voltage Gain vs Supply Voltage

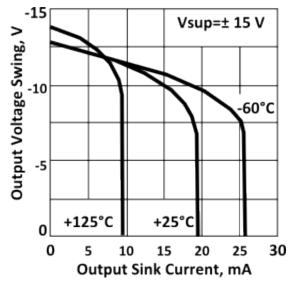

Figure 8. Output Voltage vs Output Sink Current

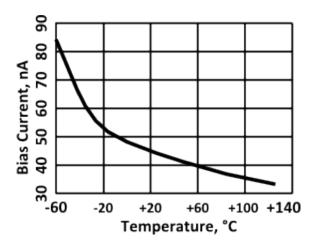

Figure 10. Input Bias Current vs Temperature

Figure 11. Cain Bandwidth vs Temperature

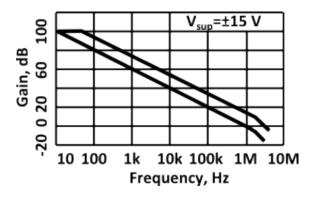

Figure 13. Open Loop Frequency Response

Figure 15. Noise Voltage & Current vs Frequency

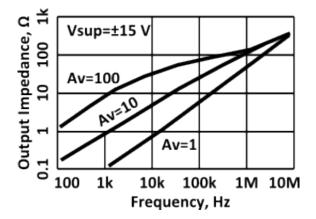

Figure 12. Output Impedance vs Frequency

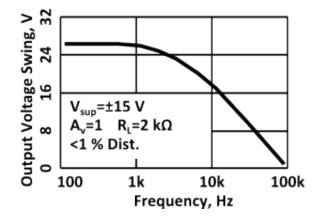

Figure 14. Undistorted Output Voltage Swing vs Frequency

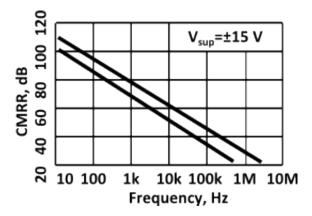

Figure 16. Common Mode Rejection Ratio vs Frequency

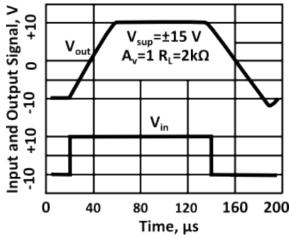

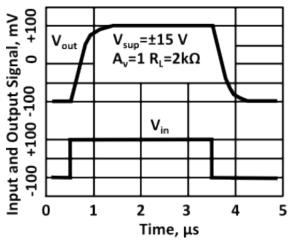

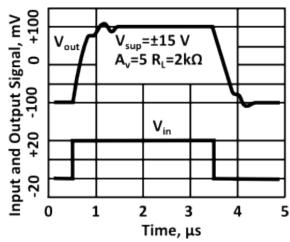

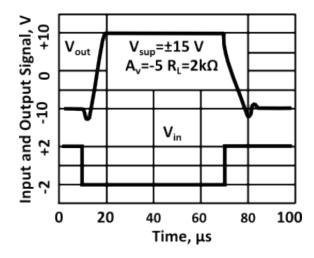

Figure 17. Large Signal Pulse Response (148)

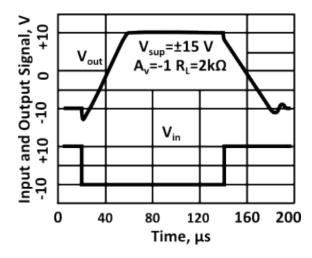

Figure 19. Small Signal Pulse Response (148)

Figure 21. Inverting Large Signal Pulse Response (148)

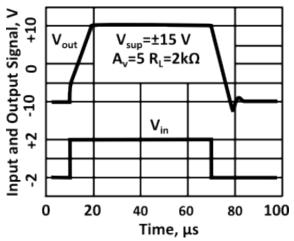

Figure 18. Large Signal Pulse Response (149)

Figure 20. Small Signal Pulse Response (149)

Figure 22. Inverting Large Signal Pulse Response (149)

The  $\alpha$ RD148 series are quad low power 741 op amps. In the proliferation of quad op amps, these are the first to offer

## **Application Hints**

the convenience of familiar, easy to use operating characteristics of the 741 op amp. In those applications where 741 op amps have been employed, the αRD148 series op amps can be employed directly with no change in circuit performance. The  $\alpha$ RD149 series has the same characteristics as the  $\alpha$ RD148 except it has been decompensated to provide a wider bandwidth. As a result the part requires a minimum gain of 5. The package pin-outs are such that the inverting input of each amplifier is adjacent to its output. In addition, the amplifier outputs are located in the corners of the package which simplifies PC board layout and minimizes package related capacitive coupling between amplifiers. The input characteristics of these amplifiers allow differential input voltages which can exceed the supply voltages. In addition, if either of the input voltages is within the operating common-mode range, the phase of the output remains correct. If the negative limit of the operating common-mode range is exceeded at both inputs, the output voltage will be positive. For input voltages which greatly exceed the maximum supply voltages, either differentially or common-mode, resistors should be placed in series with the inputs to limit the current. Like the LM741, these amplifiers can easily drive a 100 pF capacitive load throughout the entire dynamic output voltage and current range. However, if very large capacitive loads must be driven by a non-inverting unity gain amplifier, a resistor should be placed between the output (and feedback connection) and the capacitance to reduce the phase shift resulting from the capacitive loading. The output current of each amplifier in the package is limited. Short circuits from an output to either ground or the power supplies will not destroy the unit. However, if multiple output shorts occur simultaneously, the time duration should be short to prevent the unit from being destroyed as a result of excessive power dissipation in the IC chip. As with most amplifiers, care should be taken lead dress, component placement and supply decoupling in order to ensure stability. For example, resistors from the output to an input should be placed with the body close to the input to minimize "pickup" and maximize the frequency of the feedback pole which capacitance from the input to ground creates.

A feedback pole is created when the feedback around any amplifier is resistive. The parallel resistance and capacitance from the input of the device (usually the inverting input) to AC ground set the frequency of the pole. In many instances the frequency of this pole is much greater than the expected 3 dB frequency of the closed loop gain and consequently there is negligible effect on stability margin. However, if the feedback pole is less than approximately six times the expected 3 dB frequency a lead capacitor should be placed from the output to the input of the op amp. The value of the added capacitor should be such that the RC time constant of this capacitor and the resistance it parallels is greater than or equal to the original feedback pole time constant.

# **Physical Dimensions**

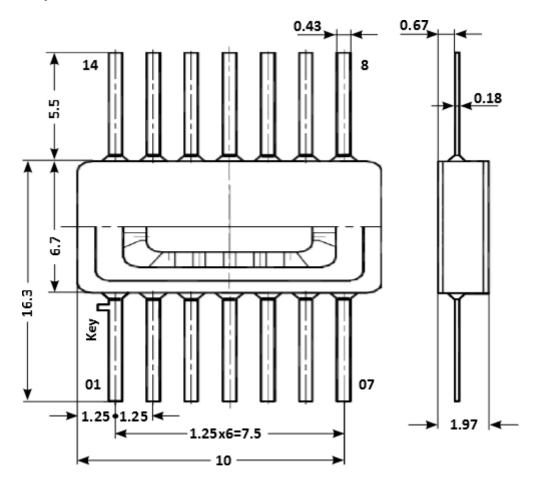

# Flatpack CSOF-14/6.7x10-1.25

#### **Notes:**

- 19. Lead finish to be 1.0  $\mu m$  minimum gold over 1.5  $\mu m$  to 8  $\mu m$  nickel underplate

- 20. Lead resistance to be 300 m $\Omega$  max

Figure 23. Ceramic Flat Package

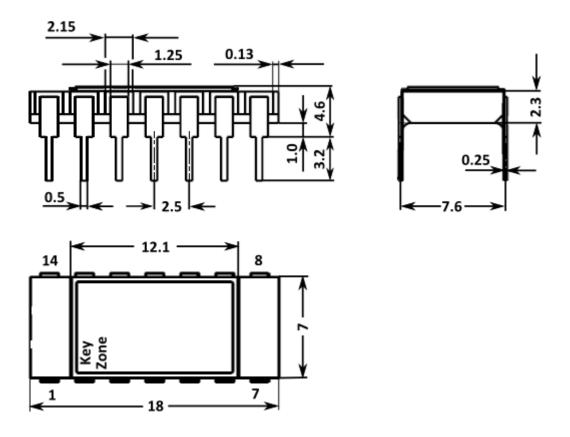

# Cerdip CDIP-14/7x18-2.5

#### **Notes:**

- 21. Lead finish to be 1.5  $\mu m$  minimum gold over 1.5  $\mu m$  to 8  $\mu m$  nickel underplate

- 22. Dimension 0.13  $\mu m$  shall be measured from the edge of the furthest extension of the metal pad or lead

- 23. Lead resistance to be 200 m $\Omega$  max

Figure 24. Ceramic DIP Package

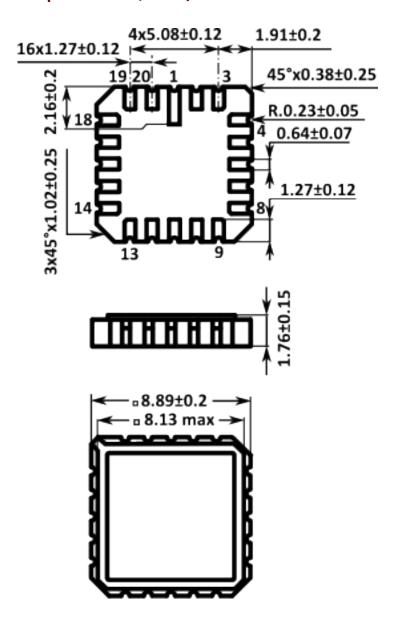

# Ceramic Leadless Chip Carrier CQFN-20/8.9x8.9-1.27

## Notes:

24. Unless otherwise specified, a minimum clearance of 0.015 inch (0.38mm) shall be maintained between all metallized features(e.g., lid, castellations, terminals, thermal pads, etc.)

Figure 25. Leadless Package

## **Revision History**

| Date     | Release | Used Documents                                                 | Changes                                                                                        | Originator |

|----------|---------|----------------------------------------------------------------|------------------------------------------------------------------------------------------------|------------|

| 09/28/12 | Α       | JEDEC JESD30E                                                  | Writing improvement, typos correction. Addition: package CQFN-20, parts αRD148XR7U, αRD149XR7U | S.Sudin    |

| 04/29/12 | 0       | АЕЯР.431130.488 ТУ<br>ОСТ 11 0694-89<br>RDm037 э3<br>RDm1002 Д | Original                                                                                       | S.Sudin    |

All RD ALFA Microelectronics semiconductor products are manufactured, assembled and tested under ISO9001 quality systems certification.

RD ALFA Microelectronics products are sold by description only. RD ALFA Microelectronics reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by RD ALFA Microelectronics is believed to be accurate and reliable. However, no responsibility is assumed by RD ALFA Microelectronics or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of RD ALFA Microelectronics or its subsidiaries. For information regarding RD ALFA Microelectronics and its products see web site <a href="http://www.rdalfa.eu">http://www.rdalfa.eu</a>.